本文是对Dr. Seung Kang的讲座Emerging Memories and Pathfinding for the Era of Sub-10nm System-on-Chip的总结与思考。图片是从视频截的,不是很清晰。

现有存储器件

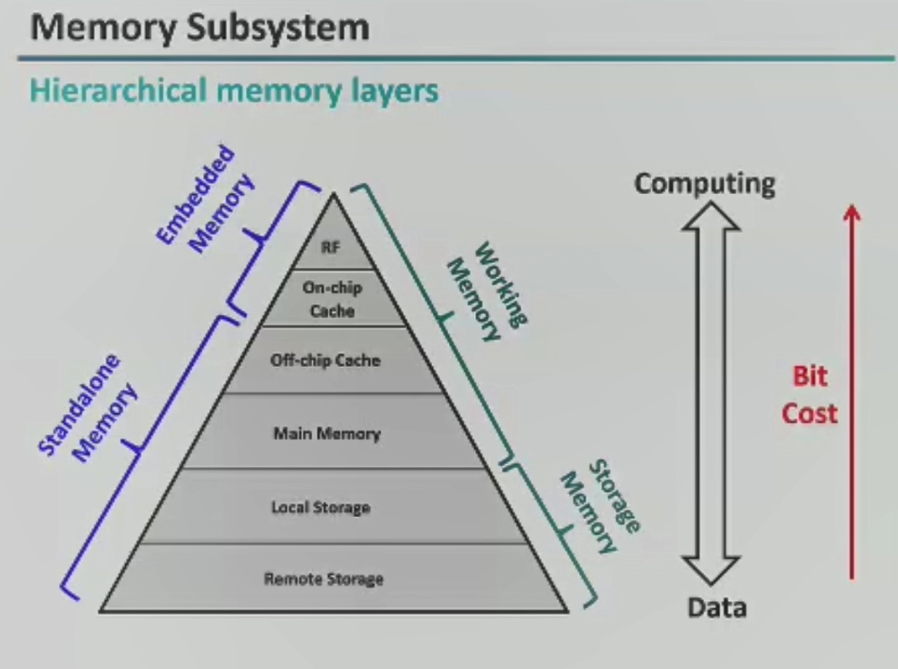

现代内存不存在通用型内存,没有哪种器件兼具速度、容量、寿命、成本上的优势,而各个器件形成了一个层级结构,各具优劣。

在上图中,每高一个层级,每比特成本大致提高十倍。工作存储器(working memory)主要看重速度和耐久性(endurance),而装载存储器(storage memory)主要看重密度(容量)和保持能力(retention)。现在各层的主流器件是:

- 寄存器堆(register file)

- 片上缓存——SRAM

- 外部缓存——嵌入式DRAM

- 主存——DRAM

- 本地存储——Flash(SSD),机械硬盘

- 远程存储——Flash(SSD),机械硬盘,磁带……

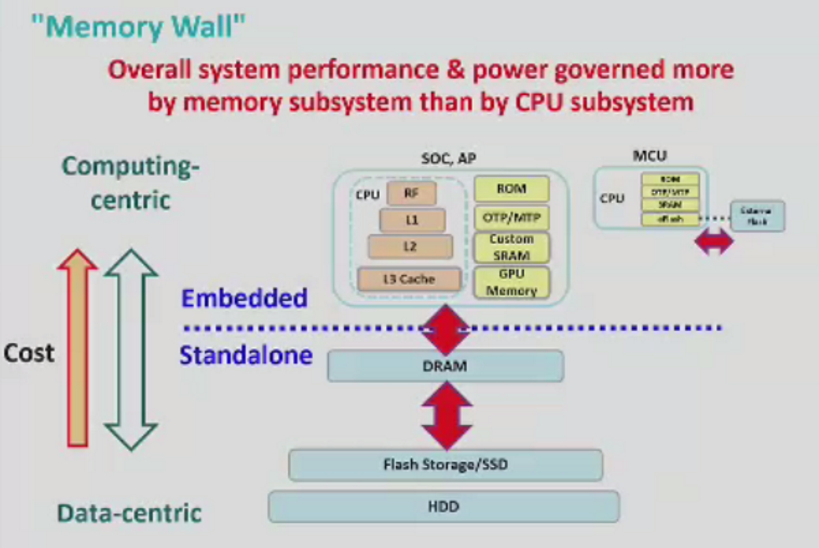

存储墙

在计算机体系架构中,存储墙的问题已十分严重。计算机的功耗和性能已经愈发受到存储器的限制。这其中的症结在于:片上存储器与主存之间的鸿沟,以及工作存储器与装载存储器之间甚至更大的性能鸿沟。

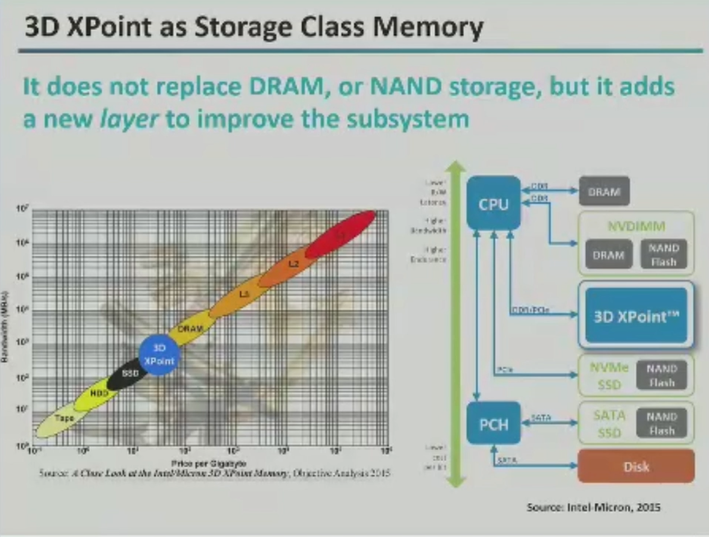

这些鸿沟造成了存储器的层级结构的缺位,造成了这些位置处产生了IO瓶颈。片上存储器与主存之间的性能差主要是主线上的延时,是架构的问题,而工作存储器与装载存储器之间则是器件导致的。在DRAM与SSD之间,Intel已发布过Optane(傲腾内存)来填补这个缺位,事实上这里还有很多器件可以填补,值得研究。

多核处理器

多核处理器中随核数增加需要大量的片上缓存。但是对于SRAM而言,其随制程的微缩前景堪忧。40nm制程上,一个6T-SRAM单元面积约为150F2,但到7nm制程时一个单元要占据550F2。此处F是集成电路特征尺寸,即器件的最小尺寸,通常情况下就是制程大小,例如65nm制程下,一个6T-SRAM单元若占据0.52um2,就是123F2(123=0.52*(1000/65)2)。也即,处理器的其它部分随集成电路工艺的提升而缩小时,SRAM的微缩速度慢了很多,导致在更先进的工艺节点上,SRAM显得愈发臃肿。

对于SRAM而言,更严重的问题在于其高待机功率。SRAM在现在的制程与容量下漏电严重,占据了处理器很大一部分功耗,限制了多核处理器的性能提升。

物联网与嵌入式系统

对嵌入式系统以至于可穿戴设备或其它物联网设备而言,功耗是个十分重要的因素。如果使用传统的冯诺依曼架构(现在的嵌入式设备也大多仍采用),将数据从存储器与处理器之间来回搬运极其浪费能量。另外易失存储器件浪费的功耗十分之多(DRAM、SRAM)。并且存储器一直是设备安全性的弱点,为了设备的安全性,非易失的存储器件也会是更好的选择。在这方面,PUF(physical unclonable function,物理不可克隆功能)与RNG(random number generator,随机数发生器)等器件的运用将是制造更安全的芯片的方法。其中PUF利用半导体元件自身独一无二的指纹保护芯片,任何探测或观测PUF操作的尝试都将改变底层电路特征,从而防范侵入式物理攻击。从内存本身硬件器件提升安全性会是一个有前景的方向。

"The IOT is an NVM problem."

Greg Yeric, ARM (2015 IEDM Plenary Talk)

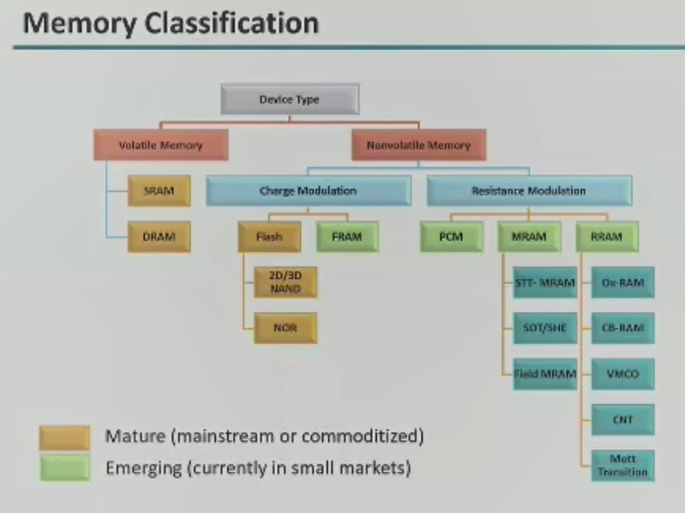

新兴存储器件

上图展示了现有的主流存储器件。黄色器件(SRAM、DRAM)都是成熟的技术。而新兴存储器件全部来自非易失存储,其中相比于传统上以电荷存储数据,我们有新兴的以电阻存储数据的方式。这些以电阻存储数据的器件有:PCM(Phase-Change Memory,相变存储器)、MRAM(Magnetoresistive Random Access Memory,磁阻式随机存储器)、RRAM(Resistive Random Access Memory,阻变存储器)。而以电荷存储数据的新兴器件有:FRAM(Ferroelectric Random Access Memory,铁电存储器)。电阻存储数据由于不需要电荷的储存放电,因而功耗较低。

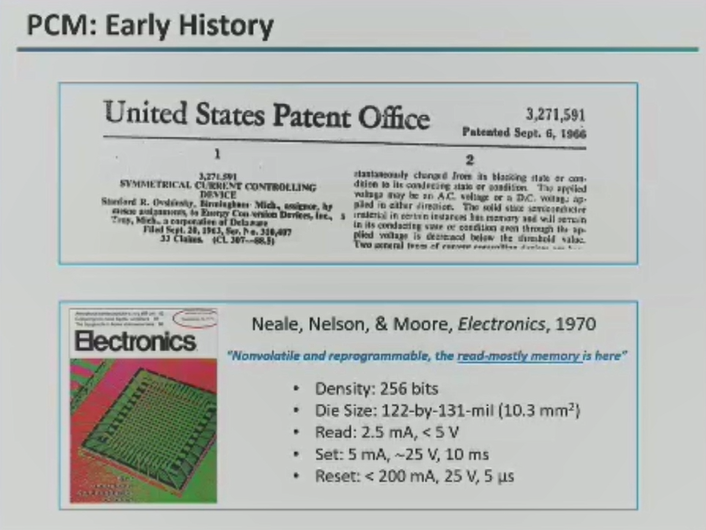

PCM

相变存储器(PCM,PC-RAM或PRAM)历史非常悠久,可以追溯至1966年。在下图这篇1970年的论文的标题中提到:"the read-mostly memory is here",表明这种器件写入较为困难,主要用于读取。

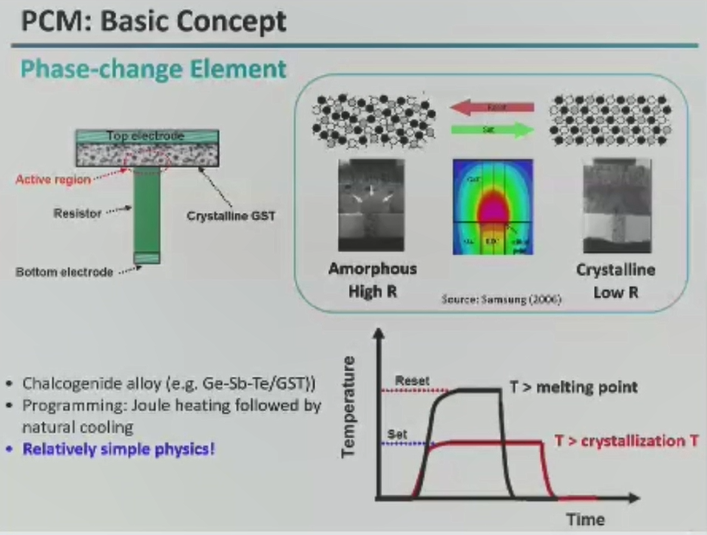

物理上而言,相变存储器原理如下:相变材料——典型的如硫族元素构成的GeSbTe合金(GST)——有非晶态和晶态两种状态,其中非晶态阻值高,晶态阻值低。从晶态转变为非晶态,我们加热材料超过熔点,然后迅速冷却。从非晶态转变为晶态,我们加热材料超过结晶温度,但低于熔点,保持一段时间使得材料结晶,然后冷却。

这种加热冷却的方式有很多技术上的问题:加热需要单位面积上充分的电流,而在更先进的工艺节点下,由单元中的辅助器件(晶体管、二极管、三极管)提供充足的电流也更加困难。同时,如何充分利用热量?如何限制热量在自身单元而不影响近邻单元?现有的相变器件的这些可靠性问题都是值得关注的。

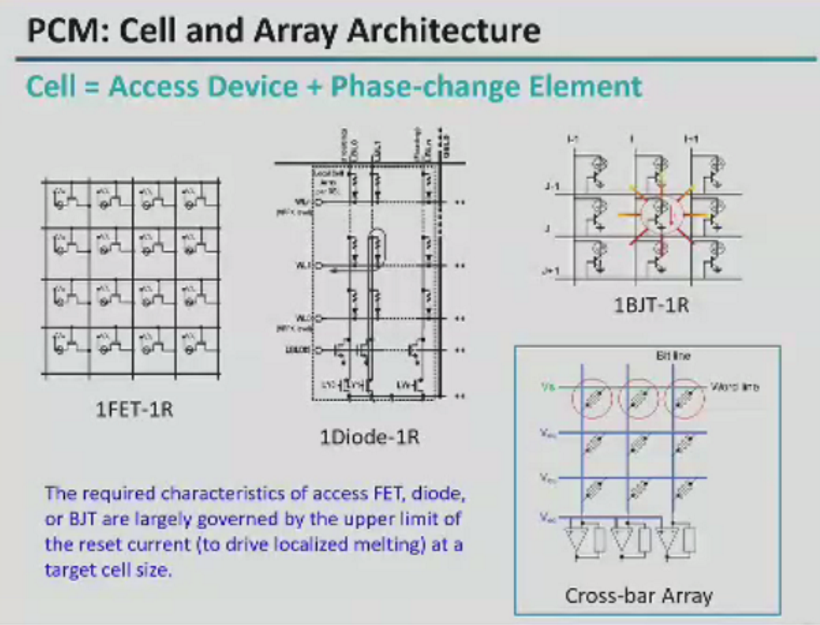

PCM单元由相变器件与读写装置构成。辅助读写可以使用晶体管、二极管、三极管,如上图所示。当然crossbar架构还是最重要的架构,直接将相变器件跨接在字线和位线上,该架构不需要晶体管,获得了更高的密度。crossbar架构需要选择器(selector)直接与元件耦合,选择器的设计也是很重要的工作。

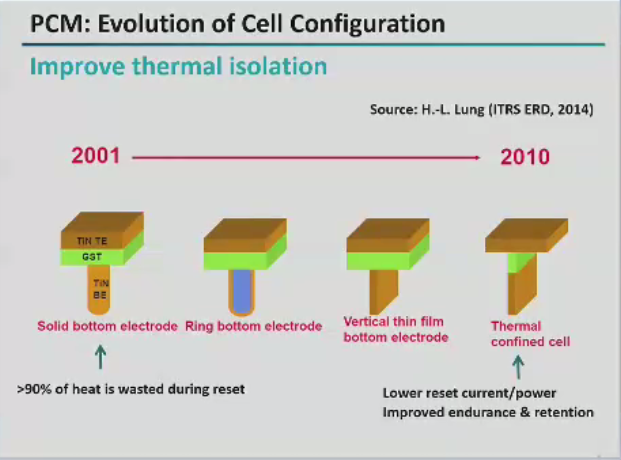

对于加热相变材料,在器件上也有所进步。早期的相变材料会浪费超过90%的热量,但现在利用更窄的电极和相变材料,可以降低写入电流以及功耗,同时也能提升器件的持久性和保持能力。

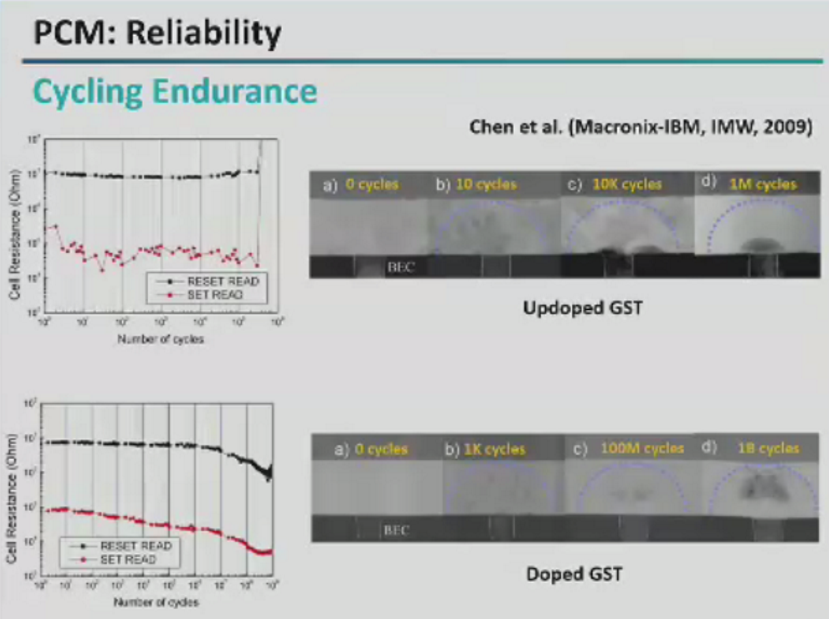

现有的相变存储器弱点在于寿命和可靠性。写入次数多了后,可见阻值开始波动,影响可靠性。这是非常容易理解的——材料不能承受反复的熔化、结晶。一般PCM大约能承受106周期,而改进器件本身性质也可以达到109周期。

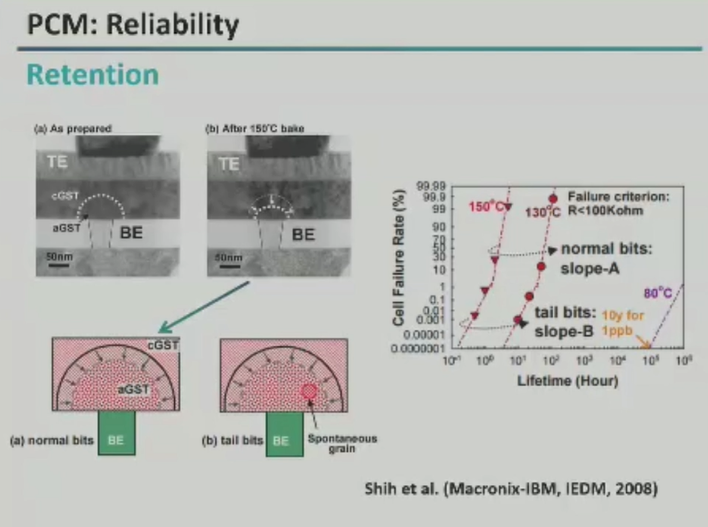

而对于相变存储器的保持能力,相变材料可能在非晶态下自行结晶(即使是在常温下),晶态也可能被破坏,现有技术也在对此加以改进,如下图工作能在80℃保持10年。

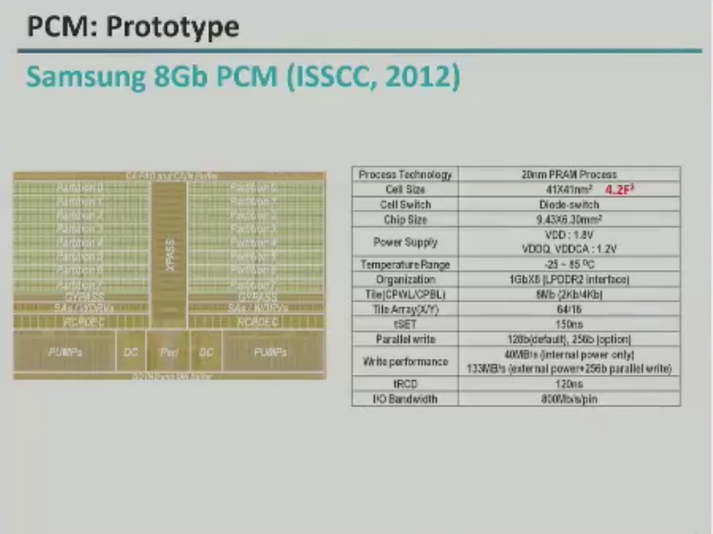

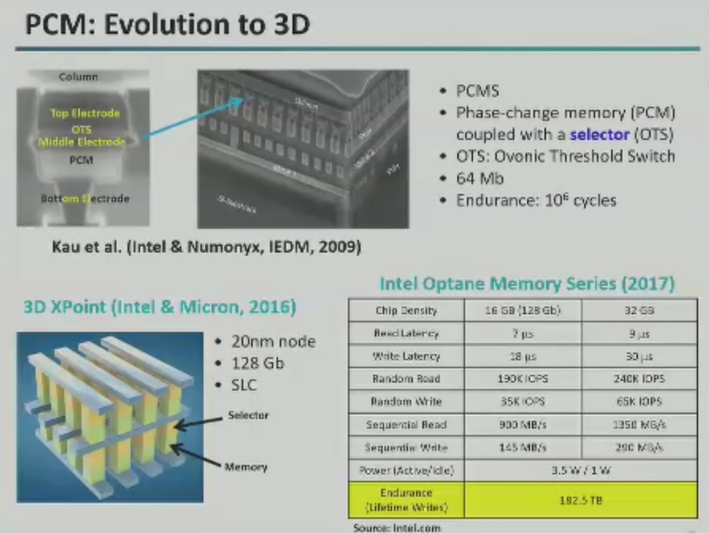

参见下图三星制造的相变存储器,可见达到了4.2F2的很小的面积(高密度),重结晶较慢,但150ns的写入速度仍比Flash快了许多。而英特尔的Optane则显得更为优秀:3D XPoint技术,而且已经商业化。3D XPoint使用crossbar架构,直接与选择器耦合,选择器用来防止潜通路电流的干扰(相邻单元电流的影响)。虽然性能强于Flash,但仍较DRAM有较大的差距,无论是在读写延时还是寿命上。

可以看到的是,3D XPoint技术填补了SSD与DRAM之间的鸿沟,可以作为存储层级的一个新的级别,用来解决性能的不匹配。

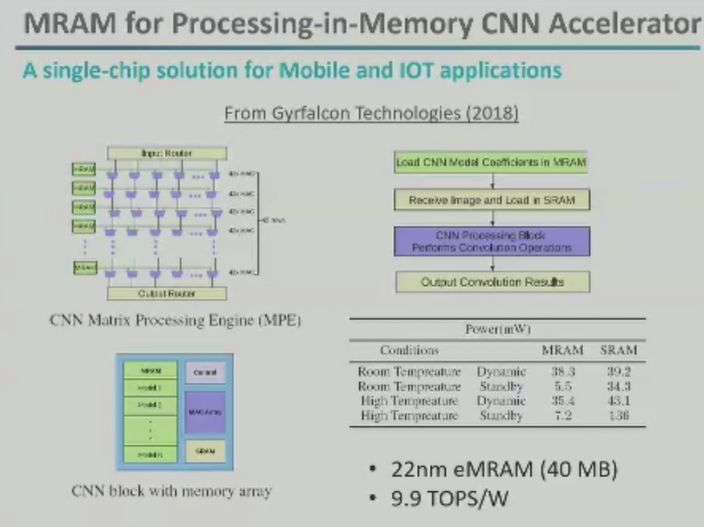

MRAM

磁阻式随机存储器(MRAM)原理上利用巨磁阻效应(Giant Magnetoresistance,GMR,2007年诺贝尔物理学奖),是指物质在一定磁场下电阻改变,而一定条件下,电阻率变化幅度相当大。而现在的新一代MRAM是自旋转移矩存储器(Spin-transfer-torque MRAM, STT-MRAM, ST-MRAM或STT-RAM)。这是一种性能很好的新兴存储器,有冲击DRAM之势。

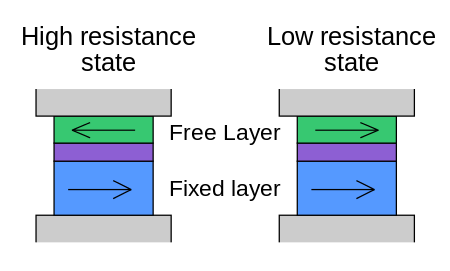

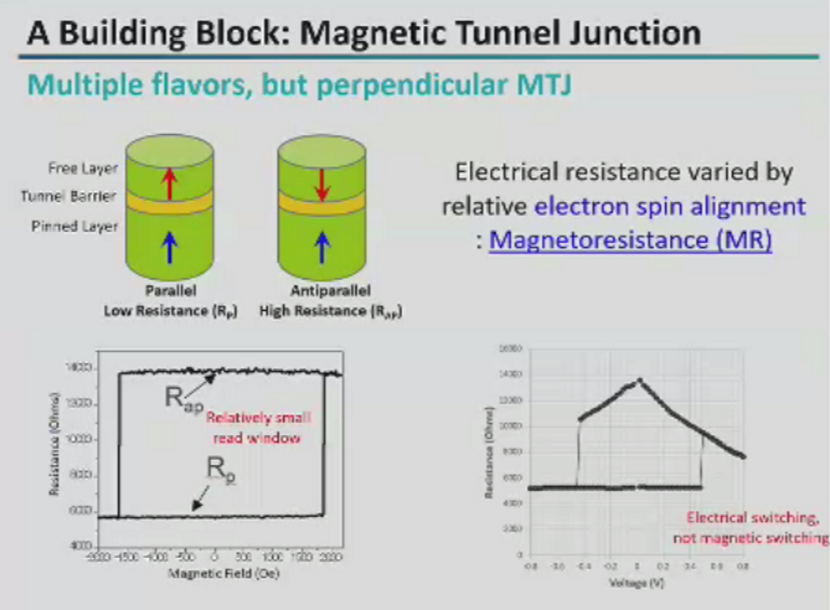

MRAM的物理原理较PCM复杂许多。可参见自旋转移矩,磁隧道结的介绍。MRAM的主要原理在于:磁隧道结(Magnetic Tunnel Junction, MTJ)中两层铁磁材料之间夹一层厚度极薄的绝缘层。两层铁磁材料一个为钉扎层,磁化方向较难改变;另一层铁磁材料为自由层,矫顽力较小,在外加磁场的作用下磁化方向容易翻转。两层材料磁化方向相反时,隧穿电流较小,电阻较大;磁化方向相同时,隧穿电流较大,电阻较小。这两种状态可以用以存储数据。而对于自旋转移矩存储器而言,使用电流而不是磁场来操纵磁化方向。将正交于铁磁层的电流通过较厚的钉扎层时,可以产生自旋极化电流。当自旋极化电流进入自由层时,自旋角动量得到转移,从而改变磁化方向。相较更传统的MRAM器件,STT-MRAM的操纵是纯电的,不必操控磁场,这对于集成电路而言更为现实。

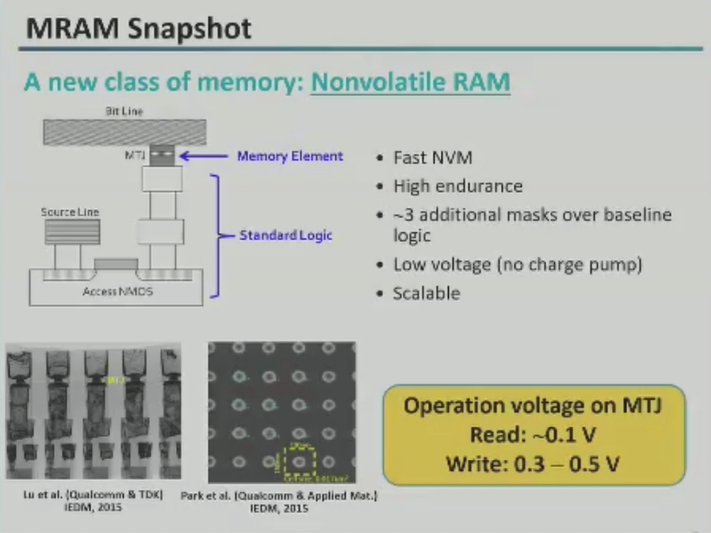

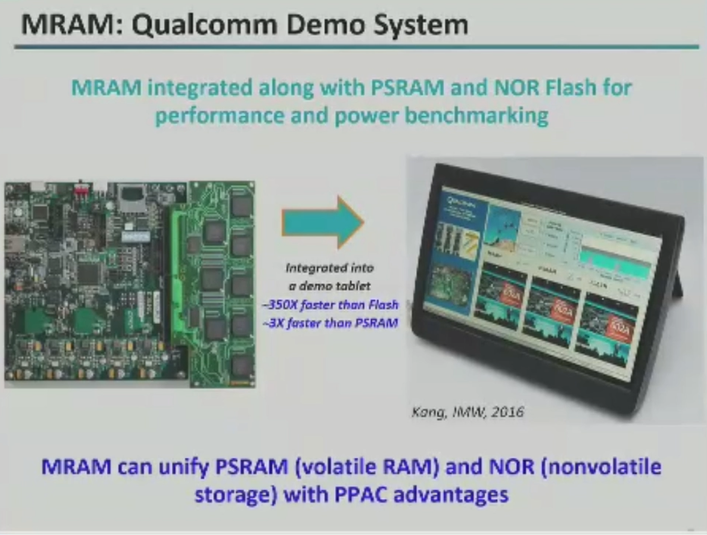

MRAM现在十分强势,它能够具有几乎可媲美DRAM甚至SRAM的速度,是非易失器件,功耗极低,持久性极长,几乎是一种通用内存。值得注意的是,它的读写电压极低,都电压只需0.1V,写电压也只需0.3-0.5V。

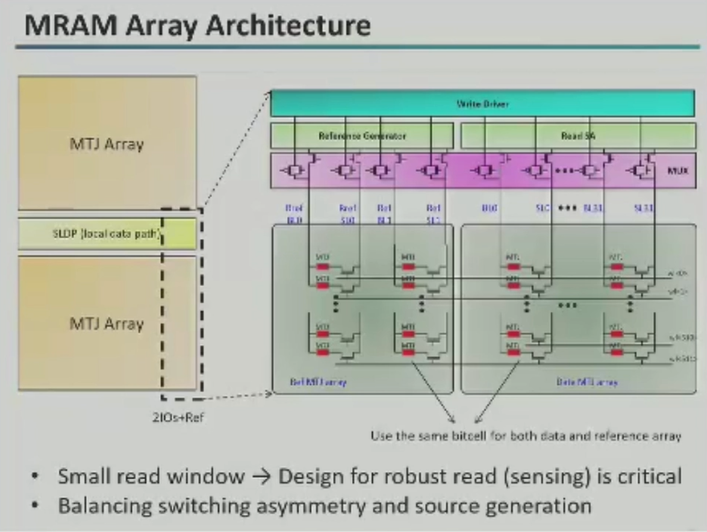

一个典型的MRAM架构如上,其与SRAM几乎一样,不同之处在于添加了一个预写入的参考阵列,来在读时对比实际单元的数据。MRAM的主要问题在于:其两个状态之间区别非常小,要准确读取必须有精确的外围电路,并且有良好的机制应对器件本身的噪音与变化,读操作必须鲁棒性强。写操作还需要晶体管用以控制,但是当MTJ这个阻性元件与晶体管耦合,接在晶体管的源极时,这形成了源极负反馈,会导致从源极驱动MTJ(磁化从反平行变为平行)的能力下降,也即是说,这时单元写入0、1是不对称的,也造成了一定困难。

另一方面,二端器件读写是同一通道的。如下图所示,我们要精细地控制读电压、写电压,使得它们互相不重叠,也不达到击穿电压。由于操作电压本身很低,这些窗口非常小。这里有两个概念:Read Disturbance Rate (RDR)和Write Error Rate (WER),前者是读操作时误进行了翻转的概率,后者是写操作时没有完成写操作的概率。在器件层面上,我们有必要实现这两个值在电压的分布上的陡变(如下图所示),这样才能给读写操作留出尽可能大的窗口。还要注意写入的时间不能过长,否则还会发生经时击穿(time dependent dielectric breakdown,TDDR)。

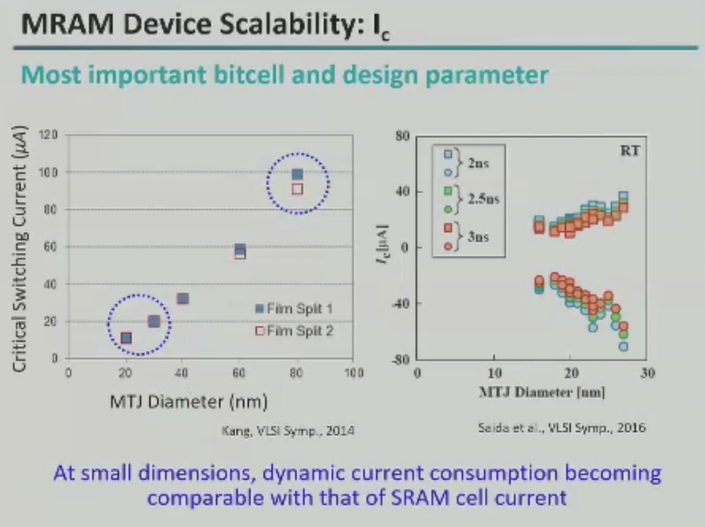

MRAM器件的缩放性能很好。更先进的工艺制程下,它需要的能量也在逐步减小,所需要的电流也在减小,与SRAM相近,只需要在几ns下提供几十uA就可以实现写入。另外,MTJ线度越小,击穿电压就更高(线度越小,电流密度更小,焦耳热更小),还提高了可靠性。但是如果要实现高密度的阵列,也是很困难的一件事情。事实上MRAM与现有的工艺不足够兼容也是主要的问题。

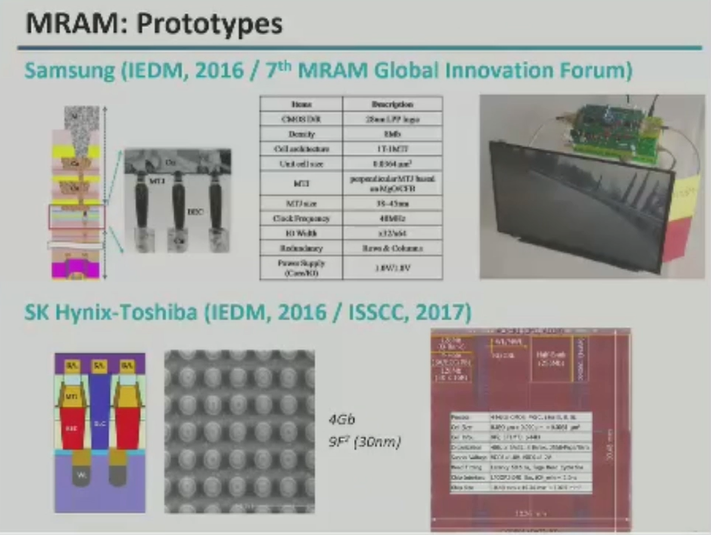

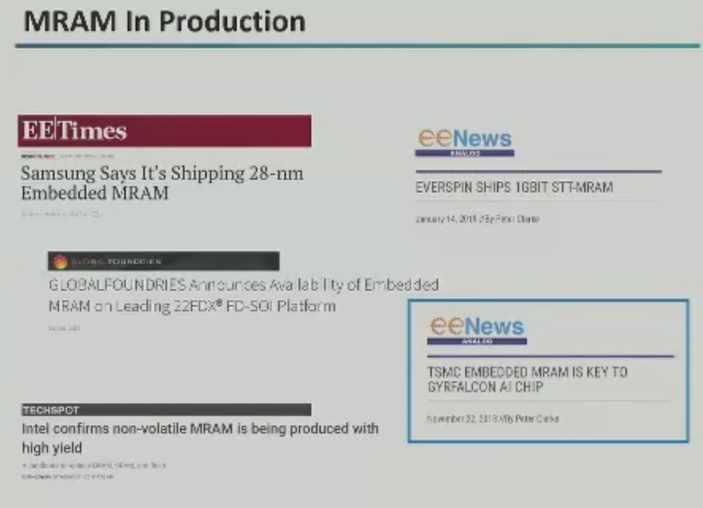

MRAM可以承受至少1015次读写周期,寿命极长,这是其用作高速缓存的重要保障。一些MRAM的实际产品如下,实际上还没有出现大容量的产品:

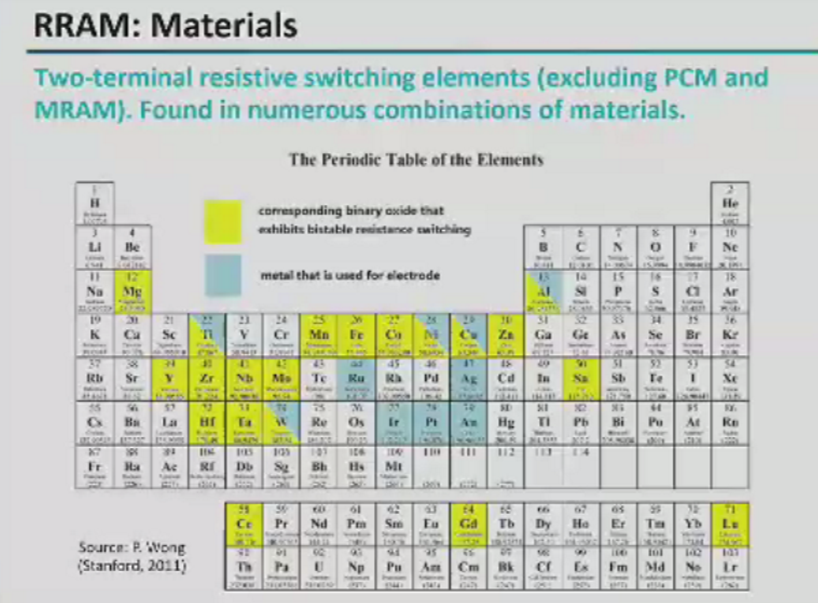

RRAM

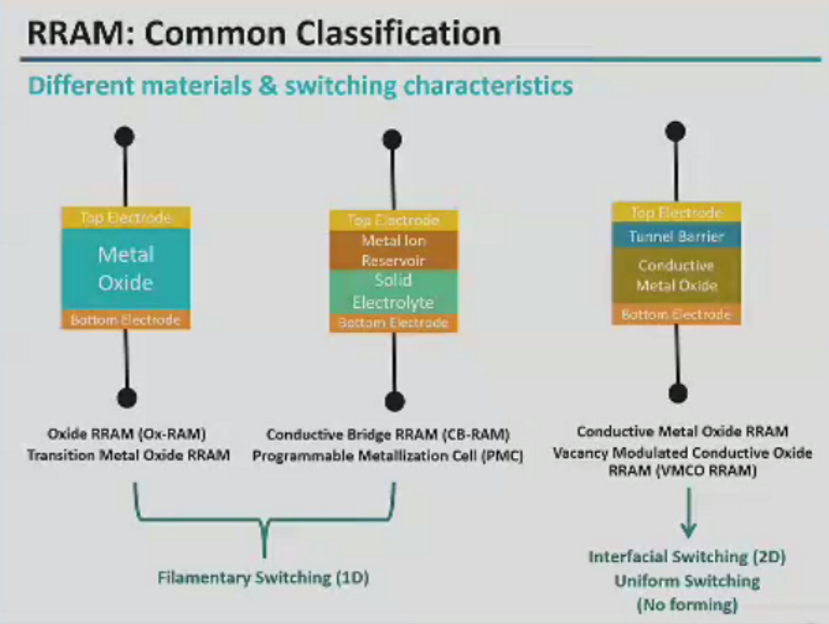

阻变存储器(RRAM或ReRAM)是指除了PCM与MRAM外的阻性可以改变的二端口元件,有大量的元素组合可以实现,如下图所示,黄色元素氧化物可呈现双稳态阻值,而蓝色元素可作电极。其中RRAM大致包括:

- 氧化物阻变存储器(Oxide RRAM,Ox-RAM):使用过渡金属氧化物夹在电极之间,空穴移动形成filament,展现两种阻态;

- 导电桥式随机存储器(Conductive Bridge RAM,CB-RAM):使用可编程金属化单元(Programmable Metallization Cell,PMC),填充固体电解质,金属离子移动产生filament;

- 空位调制导电金属氧化物阻变存储器(Vacancy Modulated Conductive Oxide RRAM,VMCO RRAM),使用导电金属氧化物加上隧道壁垒夹在电极之间。

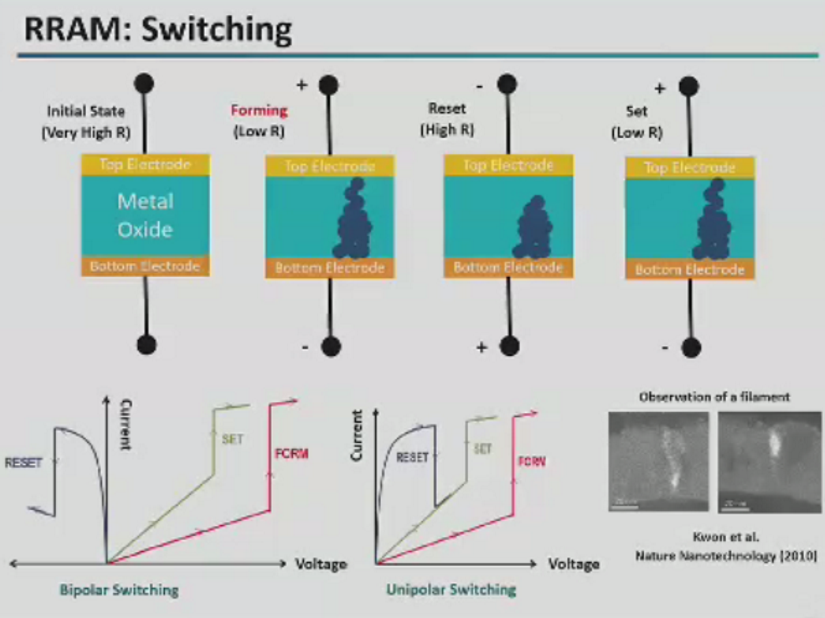

前两种器件是通过一维filament的生长改变阻态的(通过两个电极加正反电压可以生长filament或破坏之),而第三种是在界面处发生转变,是一种均匀的转变,没有filament的生长过程。实际上filament forming的原理还没有完全被理解。

对于前两种器件,如图所示,正常状态下金属氧化物绝缘,相当于电容,但在施加一个瞬时的临界电压后,局部击穿形成一个通道(filament)。此后如图,可施加正反电压破坏或重建这个通道,形成两个阻态。

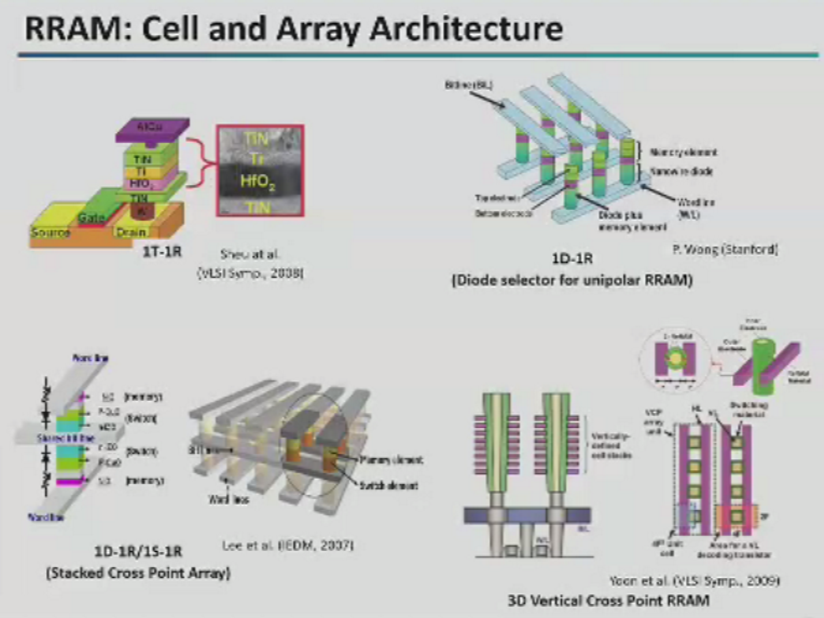

对于其架构,RRAM可以与晶体管耦合,形成1T-1R的结构(面积较大),也可以使用crossbar架构。但最重要的是,它可以较为轻松地实现3D层叠,这使得其密度潜力较大。

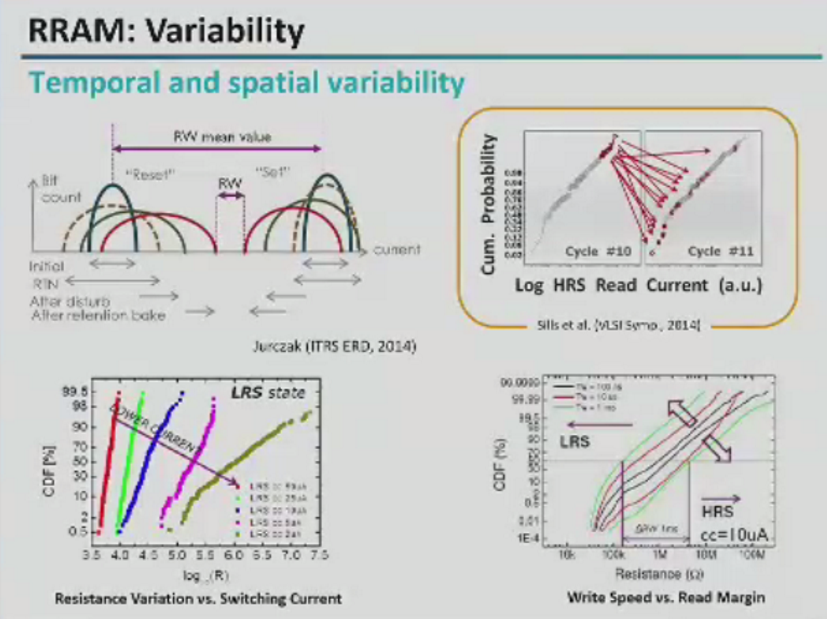

然而,由于物理机制,可以理解的是,这种器件的变异性较大。尽管与MRAM相比,其本身的读写窗口较大,但其各种因素(如热效应,干扰等)会导致电流变化范围很广,影响了读写窗口。无论是不同单元之间的差异,或者是反复读写之后造成的元件变化,都会有极大的变异性。高能耗(高电流)读写会使得读写窗口大,而追求低能耗会使得读写窗口缩小。同时慢速写也会使得读写窗口较大,快速写时读写窗口缩小。本质上这又是一个权衡利弊之事。

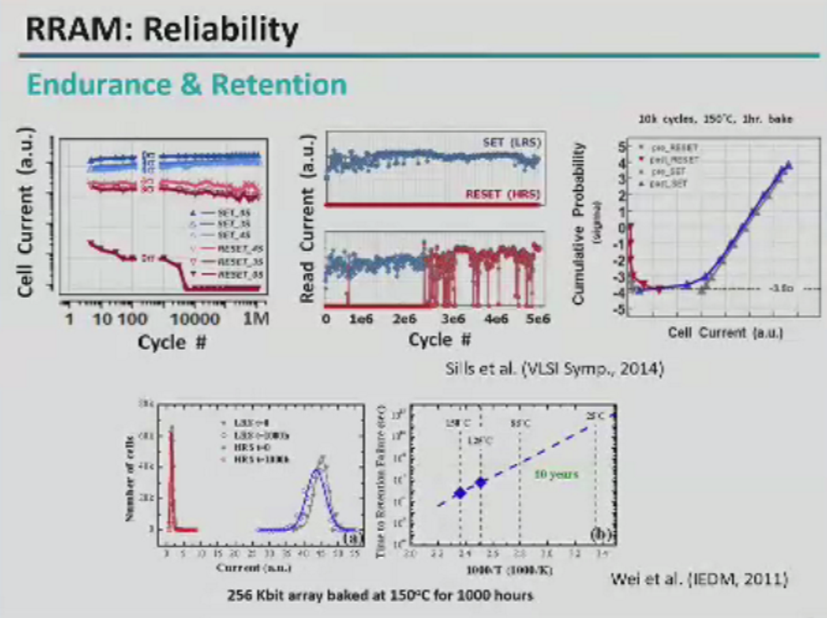

其耐久性大约只有数万或数十万个读写周期(因为控制一个原子链物理上并不能坚持很久)。但对于SSD而言,这个量级的读写周期也算足够。

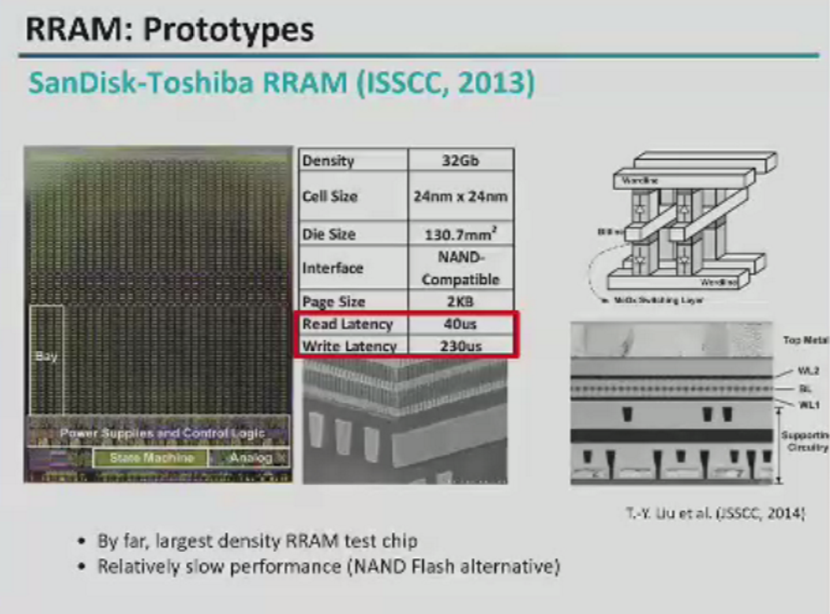

下述显示了数个RRAM产品,可以看到RRAM读写速度不够理想,但是其密度很具潜力,可能适合作为储存级存储器(storage-class memory,SCM)。

忆阻器

说到RRAM,必须提到忆阻器(memristor)。忆阻器是蔡少棠于上世纪70年代预言的,是根据四个电磁学基本量(电流、电压、电荷、磁链)提出的一种元件。这四种基本量的两两联系中,除了两个积分关系,其它已有三个基本元件代表了它们的联系(电阻——电压与电流,电容——电荷与电压,电感——磁链与电流),那么理应还有一个元件——忆阻器代表磁链与电荷之间的关系。

在2008年,惠普实现了忆阻器。自此,模拟域上,我们所能做到的事情更丰富了,忆阻器作为一种有模拟、运算性质的元件,使得存储器件的设计更加灵活,可以实现模拟量的存储器,以及可能的存算融合。

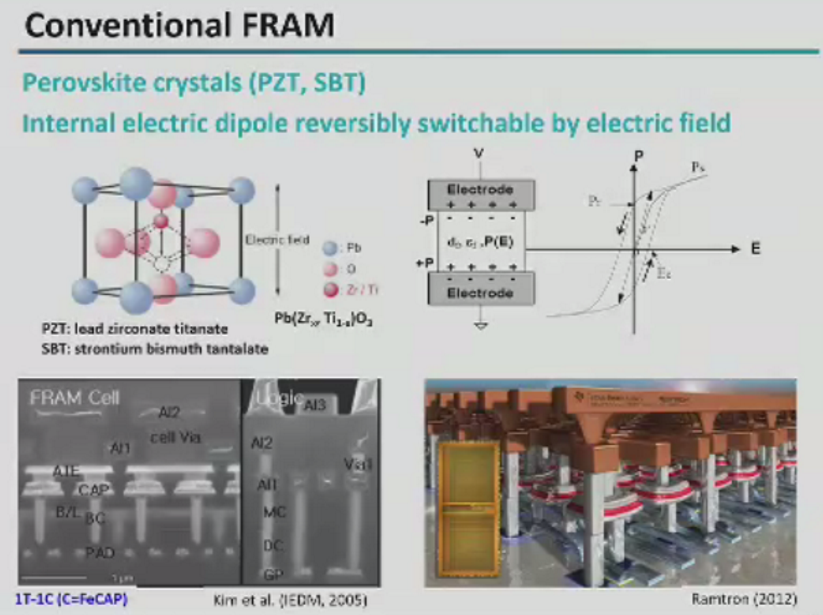

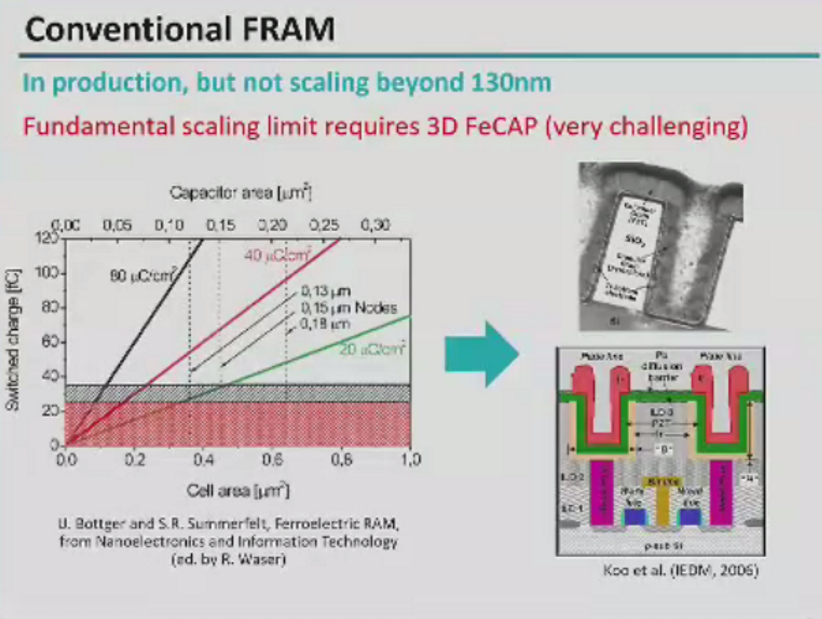

FRAM

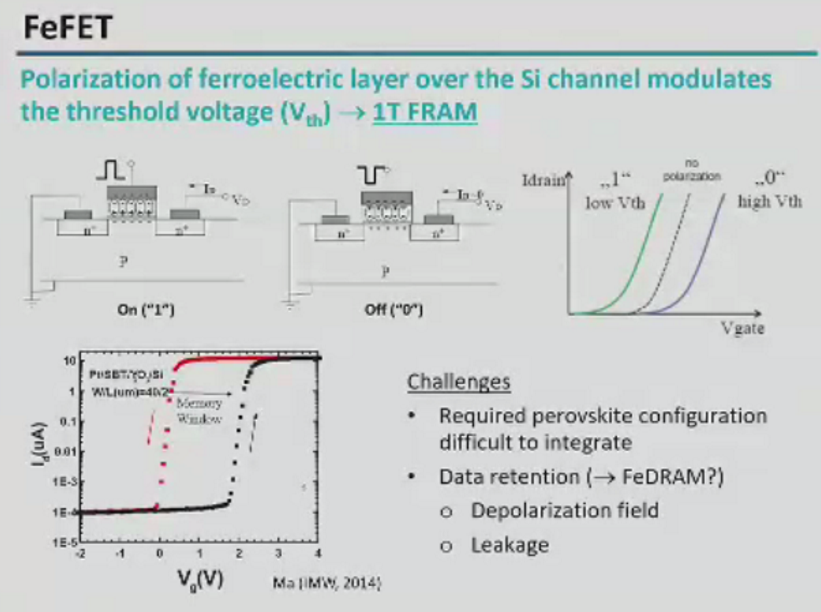

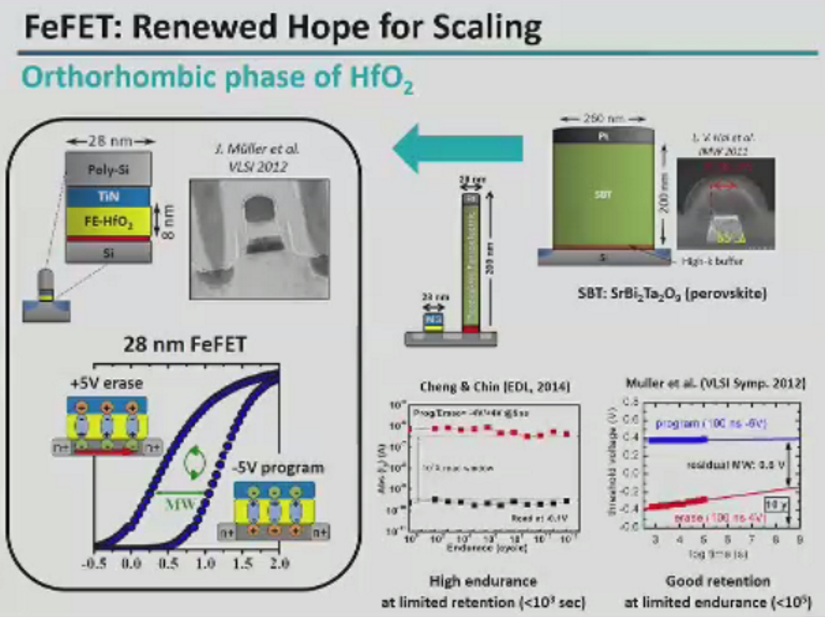

铁电存储器(FRAM或FeRAM)利用铁电材料的极化存储信息,是一种颇为古老的元件。传统的铁电材料使用钙钛矿晶体,但难以实现微缩,难以进入130nm制程。这主要是因为:铁电材料作为存储器件时存储电荷,面积更小,单位面积电荷密度更大,导致计划状态不稳定。要提高密度,可以走向3维,但挑战也十分大。

但在HfO2出现后,铁电材料重新焕发出生机。尤其是铁电晶体管(Ferroelectric FET,FeFET)的进步,其既能作为晶体管开关进行控制,又能在栅极铁电材料存储信息,是一种十分有前途的器件。

总结

新兴存储器件种类繁多,各有优缺点。如今的重点不在于寻找各方面性能优秀的通用内存,而是在于如何在不同器件之间进行选择,扬长避短。

其余暂略,有时间可能补上。